Data Sheet August 3, 2007 FN6260.4

# Dual and Quad Channel Micropower, Single Supply, Rail-to-Rail Input and Output (RRIO) Instrumentation Amplifiers

The ISL28270 and ISL28273 are dual channel micropower instrumentation amplifiers (in-amps) and the ISL28470 is a quad channel in-amp optimized for single supply operation over the +2.4V to +5.5V range.

All three devices feature an Input Range Enhancement Circuit (IREC) which maintains CMRR performance for input voltages equal to the positive supply and down to 50mV above the negative supply rail. The input signal is capable of swinging above the positive supply rail and to 10mV above the negative supply with only a slight degradation of the CMRR performance. The output operation is rail-to-rail.

The ISL28273 is compensated for a minimum gain of 10 or more. For higher gain applications, the ISL28270 and ISL28470 are compensated for a minimum gain of 100. The in-amps have bipolar input devices for best offset and excellent 1/f noise performance. The amplifiers can be operated from one lithium cell or two Ni-Cd batteries.

# Ordering Information

| PART NUMBER<br>(Note) | PART<br>MARKING     | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |  |  |  |

|-----------------------|---------------------|----------------------|----------------|--|--|--|

| ISL28270IAZ           | 28270 IAZ           | 16 Ld QSOP           | MDP0040        |  |  |  |

| ISL28270IAZ-T13*      | 28270 IAZ           | 16 Ld QSOP           | MDP0040        |  |  |  |

| ISL28273FAZ           | 28273 FAZ           | 16 Ld QSOP           | MDP0040        |  |  |  |

| ISL28273FAZ-T7*       | 28273 FAZ           | 16 Ld QSOP           | MDP0040        |  |  |  |

| ISL28470FAZ           | ISL28470 FAZ        | 28 Ld QSOP           | MDP0040        |  |  |  |

| ISL28470FAZ-T7 *      | ISL28470 FAZ        | 28 Ld QSOP           | MDP0040        |  |  |  |

| ISL28270INEVAL1Z      | Evaluation Platform |                      |                |  |  |  |

| ISL28273INEVAL1Z      | Evaluation Platform |                      |                |  |  |  |

| ISL28470EVAL1Z        | Evaluation Platform |                      |                |  |  |  |

<sup>\*</sup>Please refer to TB347 for details on reel specifications.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### **Features**

- 150µV max offset voltage (ISL28270, ISL28470)

- 600µV max offset voltage (ISL28273)

- 2.5nA max input bias current (ISL28270, ISL28470)

- 110dB CMRR

- 0.7µV/°C offset voltage temperature coefficient

- 240kHz -3dB bandwidth (G = 100) ISL28270, ISL28470

- 230kHz -3dB bandwidth (G = 10) ISL28273

- · Single supply operation

- · Rail-to-rail input and output (RRIO)

- Pb-free plus anneal available (RoHS compliant)

# **Applications**

- · Battery or solar-powered systems

- Strain gauge

- · Sensor signal conditioning

- Medical devices

- · Industrial instrumentations

#### Related Literature

- AN1289, ISL28470EVAL1Z Evaluation Board User's Guide

- AN1290, ISL2827xINEVAL1Z Evaluation Board User's Guide

- AN1298, Instrumentation Amplifier Application Note

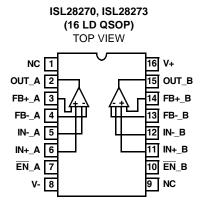

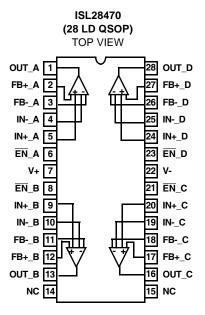

# **Pinouts**

# **Absolute Maximum Ratings** $(T_A = +25^{\circ}C)$

| Supply Voltage                                              |

|-------------------------------------------------------------|

| Supply Turn On Voltage Slew Rate 1V/µs                      |

| Input Current (IN, FB) ISL28270, ISL284705mA                |

| Differential Input Voltage (IN, FB) ISL28270, ISL28470 0.5V |

| Input Current (IN, FB) ISL28273 5mA                         |

| Differential Input (IN, FB) Voltage ISL28273 1.0V           |

| Input Voltage                                               |

| ESD Rating                                                  |

| Human Body Model                                            |

| Machine Model                                               |

#### **Thermal Information**

| Thermal Resistance                               | θ <sub>JA</sub> (°C/W) |

|--------------------------------------------------|------------------------|

| 16 Ld QSOP Package                               | 112                    |

| 28 Ld QSOP Package                               | 79                     |

| Output Short-Circuit Duration                    |                        |

| Ambient Operating Temperature Range40            | °C to +125°C           |

| Storage Temperature Range                        | °C to +150°C           |

| Operating Junction Temperature                   | +125°C                 |

| Pb-free reflow profile                           | ee link below          |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                        |

|                                                  |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

| PARAMETER                                            | DESCRIPTION                                                       | (                | CONDITIONS                    | MIN<br>(Note 1)      | TYP               | MAX<br>(Note 1)    | UNIT  |

|------------------------------------------------------|-------------------------------------------------------------------|------------------|-------------------------------|----------------------|-------------------|--------------------|-------|

| DC SPECIFICA                                         | ATIONS                                                            |                  |                               |                      |                   |                    |       |

| V <sub>OS</sub>                                      | Input Offset Voltage                                              | ISL28270, ISL284 | -150<br><b>-225</b>           | ±35                  | 150<br><b>225</b> | μV                 |       |

|                                                      |                                                                   | ISL28273         |                               | -600<br><b>-1000</b> | ±12               | 600<br><b>1000</b> | μV    |

| TCV <sub>OS</sub>                                    | Input Offset Voltage Temperature<br>Coefficient                   | Temperature = -4 | 0°C to +125°C                 |                      | 0.7               |                    | μV/°C |

| Ios                                                  | Input Offset Current between IN+ and IN-, and between FB+ and FB- | ISL28270         |                               | -1<br><b>-1.5</b>    | ±0.25             | 1<br>1.5           | nA    |

|                                                      |                                                                   | ISL28470         |                               | -1.5<br><b>-2.0</b>  | ±0.25             | 1.5<br><b>2</b>    | nA    |

|                                                      |                                                                   | ISL28273         | -1<br><b>-1.5</b>             | ±0.2                 | 1<br>1.5          | nA                 |       |

| I <sub>B</sub> Input Bias Current (IN FB- terminals) | Input Bias Current (IN+, IN-, FB+, and FB- terminals)             | ISL28270         | -2.0<br><b>-2.5</b>           | ±0.5                 | 2.0<br><b>2.5</b> | nA                 |       |

|                                                      |                                                                   | ISL28470         | -2.5<br>- <b>3.0</b>          | ±0.5                 | 2.5<br><b>3.0</b> | nA                 |       |

|                                                      |                                                                   | ISL28273         | -2.5<br>- <b>3.0</b>          | ±1                   | 2.5<br><b>3.0</b> | nA                 |       |

| R <sub>IN</sub>                                      | Input Resistance                                                  | ISL28270, ISL284 |                               | 3                    |                   | МΩ                 |       |

|                                                      |                                                                   | ISL28273         |                               | 15                   |                   | МΩ                 |       |

| V <sub>IN</sub>                                      | Input Voltage Range                                               |                  |                               | 0                    |                   | 5                  | V     |

| CMRR                                                 | Common Mode Rejection Ratio                                       | ISL28270         | V <sub>CM</sub> = 0.05V to 5V | 90                   | 110               |                    | dB    |

|                                                      |                                                                   | ISL28273         |                               | 85                   | 110               |                    | dB    |

|                                                      |                                                                   | ISL28470         |                               | 90<br><b>85</b>      | 110               |                    | dB    |

| PSRR                                                 | Power Supply Rejection Ratio                                      | ISL28270         | $V_{+} = 2.4 \text{V to 5V}$  | 90                   | 110               |                    | dB    |

|                                                      |                                                                   | ISL28273         |                               | 80<br><b>75</b>      | 95                |                    | dB    |

|                                                      |                                                                   | ISL28470         |                               | 90<br><b>65</b>      | 110               |                    | dB    |

# ISL28270, ISL28273, ISL28470

# Electrical Specifications $V_+ = +5V$ , $V_- = 0V$ $V_{CM} = 1/2V+$ , $V_{EN} = V-$ , $R_L = Open$ , $T_A = +25^{\circ}C$ , unless otherwise specified. Boldface limits apply over the operating temperature range, -40°C to +125°C. (Continued)

| PARAMETER           | DESCRIPTION                  | COND                                                    | ITIONS                     | MIN<br>(Note 1)     | TYP                | MAX<br>(Note 1)    | UNIT              |

|---------------------|------------------------------|---------------------------------------------------------|----------------------------|---------------------|--------------------|--------------------|-------------------|

| E <sub>G</sub>      | Gain Error                   | ISL28270, ISL28470                                      | $R_L = 100k\Omega$ to VCM  |                     | +0.5               |                    | %                 |

|                     |                              | ISL28273                                                |                            |                     | +0.12              |                    | %                 |

| V <sub>OUT</sub>    | Maximum Voltage Swing        | Output low, 100kΩ to 2                                  | .5V                        |                     | 4                  | 10                 | mV                |

|                     |                              | Output low, $1k\Omega$ to $2.5$                         | /                          |                     | 130                | 250<br><b>300</b>  | mV                |

|                     |                              | Output high, $100k\Omega$ to 2                          | 2.5V                       | 4.990               | 4.996              |                    | V                 |

|                     |                              | Output high, $1k\Omega$ to GN                           | ID                         | 4.75<br><b>4.70</b> | 4.88               |                    | V                 |

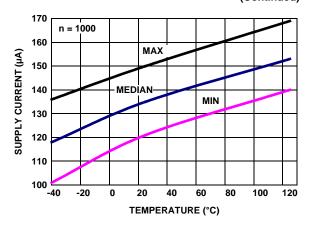

| I <sub>S,EN</sub>   | Supply Current, Enabled      | ISL28270, ISL28273 - I enabled, $\overline{EN} = V_{-}$ | Both A and B Channels      |                     | 120                | 156<br><b>195</b>  | μA                |

|                     |                              | ISL28470 - A, B, C and EN = V.                          | D Channels enabled,        |                     | 260                | 335                | μA                |

| I <sub>S,DIS</sub>  | Supply Current, Disabled     | ISL28270, ISL28273- Edisabled, $\overline{EN} = V_+$    | oth A and B Channels       |                     | 4                  | 7<br><b>9</b>      | μA                |

|                     |                              | $\frac{ISL28470 - A, B, C \text{ and }}{EN} = V_{+}$    | D Channels disabled,       |                     | 10                 | 12<br><b>15</b>    | μA                |

| V <sub>ENH</sub>    | EN Pin for Shut-down         |                                                         |                            | 2                   |                    |                    | V                 |

| V <sub>ENL</sub>    | EN Pin for Power-On          |                                                         |                            |                     |                    | 0.8                | V                 |

| I <sub>ENH</sub>    | EN Input Current High        | EN = V <sub>+</sub>                                     | <u>EN</u> = V <sub>+</sub> |                     |                    | 1<br>1.3           | μA                |

| I <sub>ENL</sub>    | EN Input Current Low         | EN = V_                                                 |                            | 26                  | 50<br><b>100</b>   | nA                 |                   |

| V <sub>SUPPLY</sub> | Supply Operating Range       | V+ to V- (Note 2)                                       | 2.4                        |                     | 5.5                | V                  |                   |

| I <sub>SC</sub>     | Short Circuit Output Current | $V_+ = 5V$ , $R_{LOAD} = 10\Omega$                      | ±20<br>±18                 | ±29                 |                    | mA                 |                   |

| AC SPECIFICA        | TIONS                        |                                                         |                            |                     |                    |                    |                   |

| SR                  | Slew Rate                    | $R_L = 1k\Omega$ to GND, ISL2                           | 0.3<br><b>0.25</b>         | 0.5                 | 0.7<br><b>0.75</b> | V/µs               |                   |

|                     |                              | $R_L = 1k\Omega$ to GND, ISL2                           | 28273                      | 0.35<br><b>0.3</b>  | 0.6                | 0.75<br><b>0.8</b> |                   |

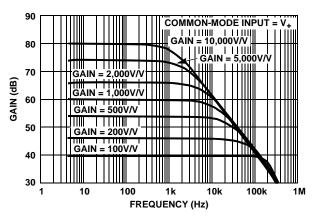

| -3dB BW             | -3dB Bandwidth               | ISL28270, ISL28470                                      | Gain = 100                 |                     | 240                |                    | kHz               |

|                     |                              |                                                         | Gain = 200                 |                     | 84                 |                    | kHz               |

|                     |                              |                                                         | Gain = 500                 |                     | 30                 |                    | kHz               |

|                     |                              |                                                         | Gain = 1000                |                     | 13                 |                    | kHz               |

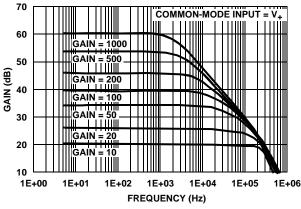

|                     |                              | ISL28273                                                | Gain = 10                  |                     | 265                |                    | kHz               |

|                     |                              |                                                         | Gain = 20                  |                     | 100                |                    | kHz               |

|                     |                              |                                                         | Gain = 50                  |                     | 25                 |                    | kHz               |

|                     |                              |                                                         | Gain = 100                 |                     | 13                 |                    | kHz               |

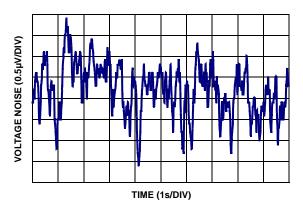

| e <sub>N</sub>      | Input Noise Voltage          | ISL28270, ISL28470                                      | f = 0.1Hz to 10Hz          |                     | 3.5                |                    | μV <sub>P-P</sub> |

|                     |                              | ISL28273                                                |                            |                     | 3.5                |                    | μV <sub>P-P</sub> |

|                     | Input Noise Voltage Density  | ISL28270, ISL28470                                      | f <sub>O</sub> = 1kHz      |                     | 60                 |                    | nV/√Hz            |

|                     |                              | ISL28273                                                |                            |                     | 210                |                    | nV/√Hz            |

#### **Electrical Specifications**

$V_+$  = +5V,  $V_-$  = 0V  $V_{CM}$  = 1/2V+,  $V_{EN}$  = V-,  $R_L$  = Open,  $T_A$  = +25°C, unless otherwise specified. Boldface limits apply over the operating temperature range, -40°C to +125°C. (Continued)

| PARAMETER      | DESCRIPTION                                    | CONDI              | MIN<br>(Note 1)                                            | TYP | MAX<br>(Note 1) | UNIT |        |

|----------------|------------------------------------------------|--------------------|------------------------------------------------------------|-----|-----------------|------|--------|

| i <sub>N</sub> | Input Noise Current Density                    | ISL28270, ISL28470 | f <sub>O</sub> = 1kHz                                      |     | 0.37            |      | pA/√Hz |

|                |                                                | ISL28273           |                                                            |     | 0.75            |      | pA/√Hz |

| CMRR @         | Input Common Mode Rejection Ratio              | ISL28270, ISL28470 | V <sub>CM</sub> = 1V <sub>P-P</sub> ,                      |     | 100             |      | dB     |

| 60Hz           |                                                | ISL28273           | $R_L = 10k\Omega$ to $V_{CM}$                              |     | 83              |      |        |

| PSRR+ @        | Power Supply Rejection Ratio (V <sub>+</sub> ) | ISL28270, ISL28470 | $V_{+}, V_{-} = \pm 1.2V, \pm 2.5V,$                       |     | 96              |      | dB     |

| 120Hz          |                                                | ISL28273           | $V_{SOURCE} = 1V_{P-P}$ ,<br>$R_L = 10k\Omega$ to $V_{CM}$ |     | 77              |      | dB     |

| PSRR- @        | Power Supply Rejection Ratio (V <sub>-</sub> ) | ISL28270, ISL28470 | $V_+$ , $V = \pm 1.2V$ , $\pm 2.5V$ ,                      |     | 105             |      | dB     |

| 120Hz          |                                                | ISL28273           | $V_{SOURCE} = 1V_{P-P}$ ,<br>$R_L = 10kΩ$ to $V_{CM}$      |     | 84              |      | dB     |

#### NOTE:

- 1. Parts are 100% tested at +25°C. Over temperature limits established by characterization and are not production tested.

- 2. V<sub>SUPPLY</sub> = +5.25V max when V<sub>ENL</sub> = +V (device in disable state).

# Typical Performance Curves

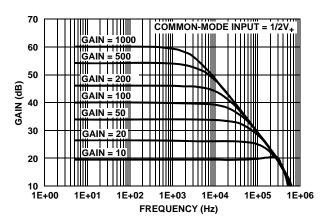

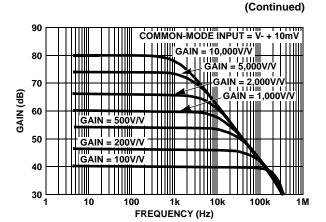

$V_{+}$  = +5V,  $V_{-}$  = 0V  $V_{CM}$  = 1/2 $V_{+}$ ,  $V_{EN}$  = V-,  $R_{L}$  = Open,  $T_{A}$  = +25°C, unless otherwise specified.

FIGURE 1. ISL28270, ISL28470 FREQUENCY RESPONSE vs CLOSED LOOP GAIN,  $V_{CM} = V_{+} = 5V$

FIGURE 2. ISL28273 FREQUENCY RESPONSE vs CLOSED LOOP GAIN,  $V_{CM} = V_{+} = 5V$

FIGURE 3. ISL28270, ISL28470 FREQUENCY RESPONSE vs CLOSED LOOP GAIN.  $V_+ = 5V$ ,  $V_{CM} = 1/2V_+$

FIGURE 4. ISL28273 FREQUENCY RESPONSE vs CLOSED LOOP GAIN.  $V_+ = 5V$ ,  $V_{CM} = 1/2V_+$

intersil FN6260.4

August 3, 2007

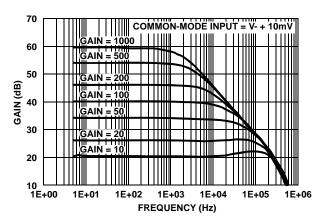

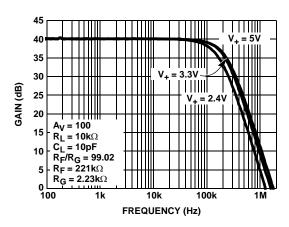

$V_{+}$  = +5V,  $V_{-}$  = 0V  $V_{CM}$  = 1/2 $V_{+}$ ,  $V_{EN}$  = V-,  $R_{L}$  = Open,  $T_{A}$  = +25°C, unless otherwise specified.

FIGURE 5. ISL28270, ISL28470 FREQUENCY RESPONSE vs CLOSED LOOP GAIN,  $V_+ = 5V$ ,  $V_{CM} = 10 \text{mV}$

FIGURE 6. ISL28273 FREQUENCY RESPONSE vs CLOSED LOOP GAIN,  $V_+ = 5V$ ,  $V_{CM} = 10 \text{mV}$

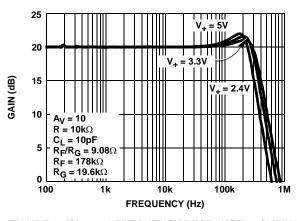

FIGURE 7. ISL28270, ISL28470 FREQUENCY RESPONSE vs SUPPLY VOLTAGE

FIGURE 8. ISL28273 FREQUENCY RESPONSE vs SUPPLY VOLTAGE

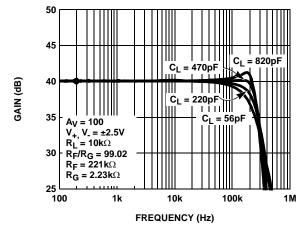

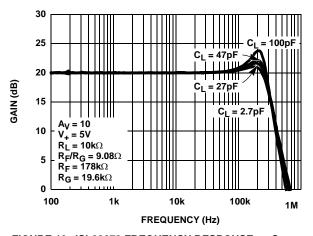

FIGURE 9. ISL28270, ISL28470 FREQUENCY RESPONSE vs C<sub>LOAD</sub>

FIGURE 10. ISL28273 FREQUENCY RESPONSE vs  $C_{\mathsf{LOAD}}$

FN6260.4

August 3, 2007

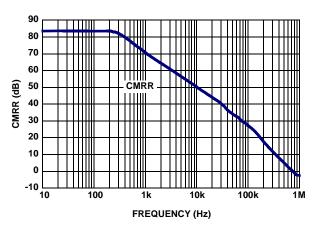

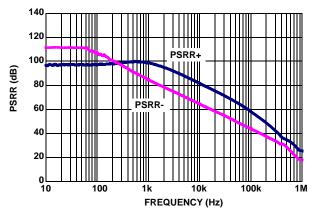

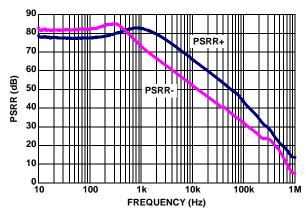

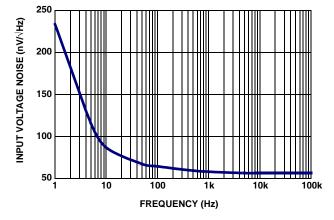

$V_{+} = +5 \text{V}, \ V_{-} = 0 \text{V V}_{CM} = 1/2 \text{V}_{+}, \ V_{EN} = \text{V-}, \ \text{R}_{L} = \text{Open}, \ \text{T}_{A} = +25 ^{\circ}\text{C}, \ \text{unless otherwise specified}.$

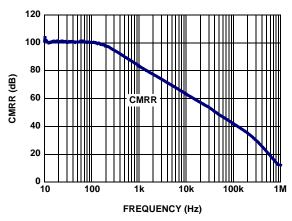

FIGURE 11. ISL28270, ISL28470 CMRR vs FREQUENCY

FIGURE 12. ISL28273 CMRR vs FREQUENCY

FIGURE 13. ISL28270, ISL28470 PSRR vs FREQUENCY

FIGURE 14. ISL28273 PSRR vs FREQUENCY

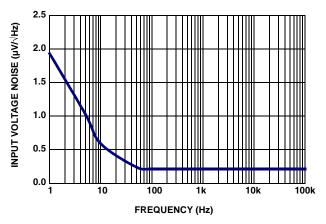

FIGURE 15. ISL28270, ISL28470 INPUT VOLTAGE NOISE SPECTRAL DENSITY (GAIN = 100)

FIGURE 16. ISL28273 INPUT VOLTAGE NOISE SPECTRAL DENSITY (GAIN = 10)

$V_{+} = +5 \text{V}, \ V_{-} = 0 \text{V V}_{CM} = 1/2 \text{V}_{+}, \ V_{EN} = \text{V-}, \ \text{R}_{L} = \text{Open}, \ \text{T}_{A} = +25 ^{\circ}\text{C}, \ \text{unless otherwise specified}.$

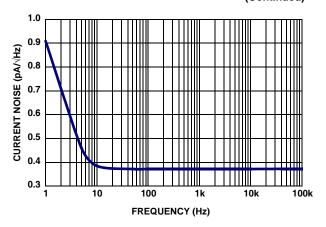

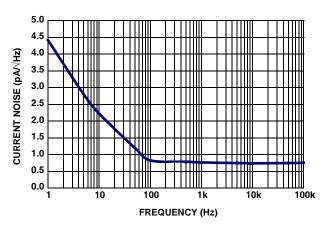

FIGURE 17. ISL28270, ISL28470 INPUT CURRENT NOISE SPECTRAL DENSITY (GAIN = 100)

FIGURE 18. ISL28273 INPUT CURRENT NOISE SPECTRAL DENSITY (GAIN = 10)

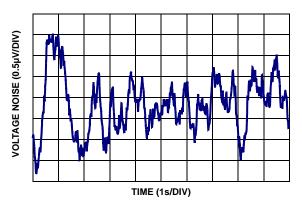

FIGURE 19. ISL28270, ISL28470 0.1Hz TO 10Hz INPUT VOLTAGE NOISE (GAIN = 100)

FIGURE 20. ISL28273 0.1Hz TO 10Hz INPUT VOLTAGE NOISE (GAIN = 10)

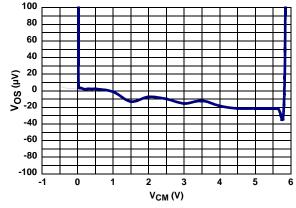

FIGURE 21. INPUT OFFSET VOLTAGE vs COMMON MODE VOLTAGE,  $V_+ = 5V$

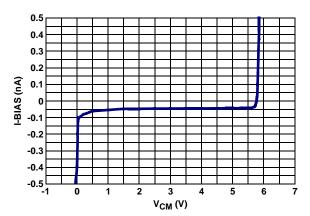

FIGURE 22. INPUT BIAS CURRENT vs COMMON MODE VOLTAGE,  $V_+ = 5V$

$V_{+} = +5 \text{V}, \ V_{-} = 0 \text{V V}_{CM} = 1/2 \text{V}_{+}, \ V_{EN} = \text{V-}, \ \text{R}_{L} = \text{Open}, \ \text{T}_{A} = +25 ^{\circ}\text{C}, \ \text{unless otherwise specified}.$

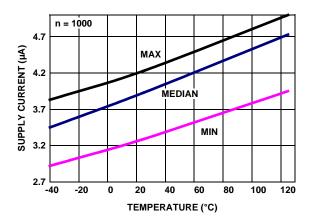

FIGURE 23. ENABLED SUPPLY CURRENT (CHANNEL A AND CHANNEL B) vs TEMPERATURE,  $V_+$ ,  $V_- = \pm 2.5V$ ,  $V_{IN} = 0V$ ,  $R_L = INF$

FIGURE 24. DISABLED SUPPLY CURRENT (CHANNEL A AND CHANNEL B) vs TEMPERATURE, V<sub>+</sub>, V<sub>-</sub> = ±2.5V, V<sub>FN</sub> = V<sub>+</sub>, V<sub>IN</sub> = 0V, R<sub>L</sub> = INF

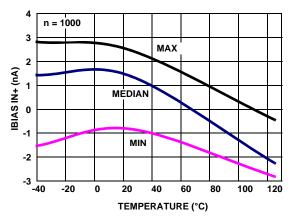

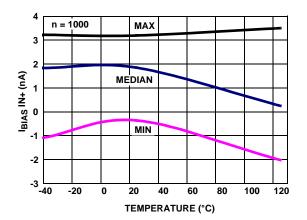

FIGURE 25. I<sub>BIAS</sub> IN+ vs TEMPERATURE, V<sub>+</sub>, V<sub>-</sub> = ±2.5V

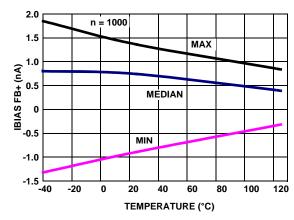

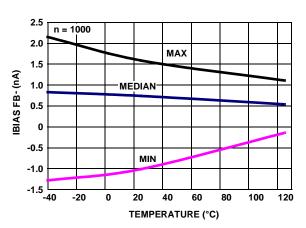

FIGURE 26.  $I_{BIAS}$  FB+ vs TEMPERATURE,  $V_+$ ,  $V_- = \pm 2.5V$

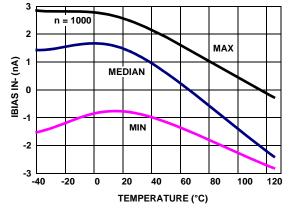

FIGURE 27.  $I_{BIAS}$  IN- vs TEMPERATURE,  $V_{+}$ ,  $V_{-} = \pm 2.5V$

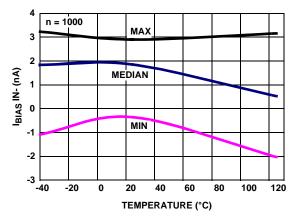

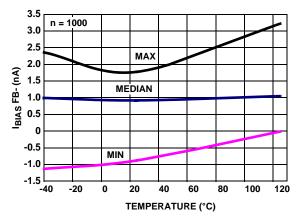

FIGURE 28. I<sub>BIAS</sub> FB- vs TEMPERATURE, V<sub>+</sub>, V<sub>-</sub> = ±2.5V

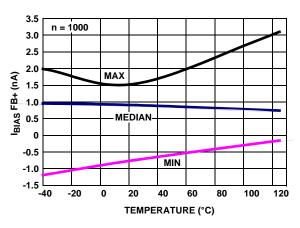

$V_+ = +5V$ ,  $V_- = 0V$   $V_{CM} = 1/2V_+$ ,  $V_{EN} = V_-$ ,  $R_L = Open$ ,  $T_A = +25$ °C, unless otherwise specified. (Continued)

FIGURE 29.  $I_{BIAS}$  IN+ vs TEMPERATURE,  $V_+$ ,  $V_- = \pm 1.2V$

FIGURE 30. IBIAS FB+ vs TEMPERATURE, V<sub>+</sub>, V<sub>-</sub> = ±1.2V

FIGURE 31.  $I_{BIAS}$  IN- vs TEMPERATURE,  $V_+$ ,  $V_- = \pm 1.2V$

FIGURE 32.  $I_{BIAS}$  FB- vs TEMPERATURE,  $V_+$ ,  $V_- = \pm 1.2V$

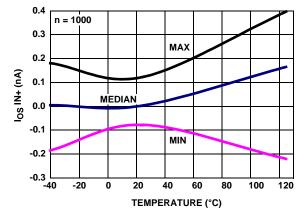

FIGURE 33.  $I_{OS}$  IN+ vs TEMPERATURE,  $V_+$ ,  $V_- = \pm 2.5V$

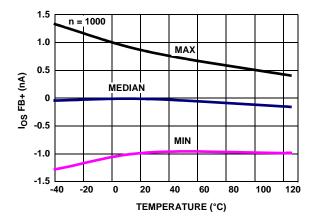

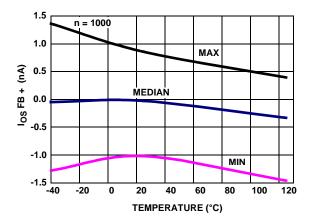

FIGURE 34.  $I_{OS}$  FB+ vs TEMPERATURE,  $V_+$ ,  $V_- = \pm 2.5V$

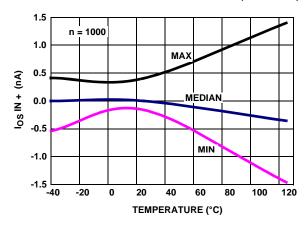

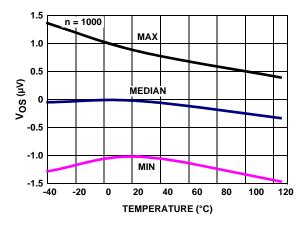

$V_{+} = +5 \text{V}, \ V_{-} = 0 \text{V V}_{CM} = 1/2 \text{V}_{+}, \ V_{EN} = \text{V-}, \ \text{R}_{L} = \text{Open}, \ \text{T}_{A} = +25 ^{\circ}\text{C}, \ \text{unless otherwise specified}.$

#### (Continued)

FIGURE 35.  $I_{OS}$  IN+ vs TEMPERATURE,  $V_+$ ,  $V_- = \pm 1.2V$

FIGURE 36. I<sub>OS</sub> FB+ vs TEMPERATURE, V<sub>+</sub>, V<sub>-</sub> = ±1.2V

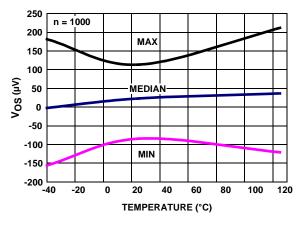

FIGURE 37. ISL28270, ISL28470  $V_{OS}$  vs TEMPERATURE,  $V_+, V_- = \pm 2.5 V$

FIGURE 38. ISL28270, ISL28470  $V_{OS}$  vs TEMPERATURE,  $V_+, V_- = \pm 1.2 V$

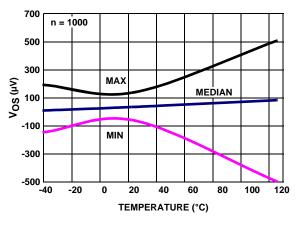

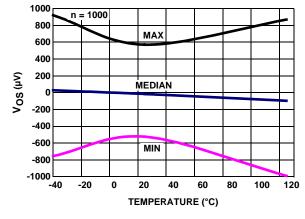

FIGURE 39. ISL28273  $V_{OS}$  vs TEMPERATURE,  $V_+$ ,  $V_- = \pm 2.5 V$

FIGURE 40. ISL28273  $V_{OS}$  vs TEMPERATURE,  $V_+$ ,  $V_- = \pm 1.2V$

FN6260.4 August 3, 2007

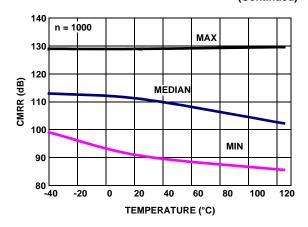

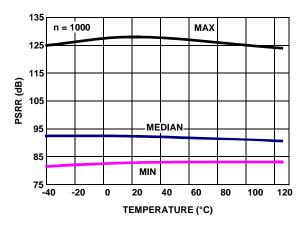

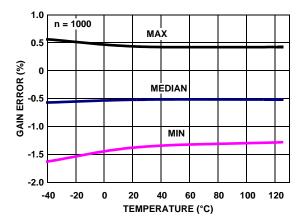

$V_{+}$  = +5V,  $V_{-}$  = 0V  $V_{CM}$  = 1/2 $V_{+}$ ,  $V_{EN}$  = V-,  $R_{L}$  = Open,  $T_{A}$  = +25°C, unless otherwise specified.

FIGURE 41. CMRR vs TEMPERATURE, VCM = +2.5V TO -2.5V,  $V_{+}$ ,  $V_{-}$  =  $\pm2.5V$

FIGURE 42. PSRR vs TEMPERATURE, V<sub>+</sub>, V<sub>-</sub> = ±1.2V TO ±2.5V

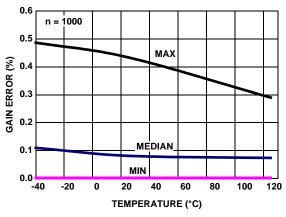

FIGURE 43. ISL28270, ISL28470 % GAIN ERROR vs TEMPERATURE,  $R_L$  = 100k

FIGURE 44. ISL28273 % GAIN ERROR vs TEMPERATURE,  $R_L$  = 100k

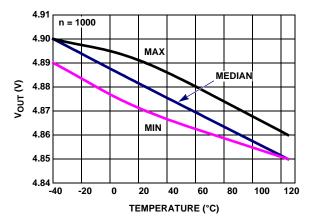

FIGURE 45. VOUT HIGH vs TEMPERATURE,  $R_L = 1k$ ,  $V_+$ ,  $V_- = \pm 2.5V$

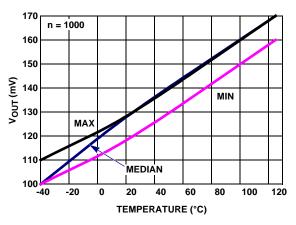

FIGURE 46. VOUT LOW vs TEMPERATURE,  $R_L = 1k$ ,  $V_+, V_- = \pm 2.5V$

$V_+ = +5V$ ,  $V_- = 0V$   $V_{CM} = 1/2V_+$ ,  $V_{EN} = V_-$ ,  $R_L = Open$ ,  $T_A = +25$ °C, unless otherwise specified. (Continued)

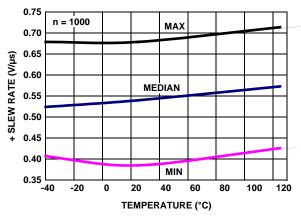

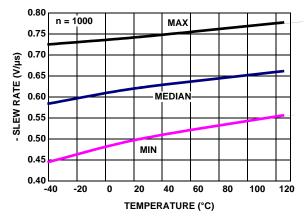

FIGURE 47. + SLEW RATE vs TEMPERATURE, INPUT = ±0.015V AT GAIN = +10

FIGURE 48. - SLEW RATE vs TEMPERATURE, INPUT = ±0.15V AT GAIN = +10

# Pin Descriptions

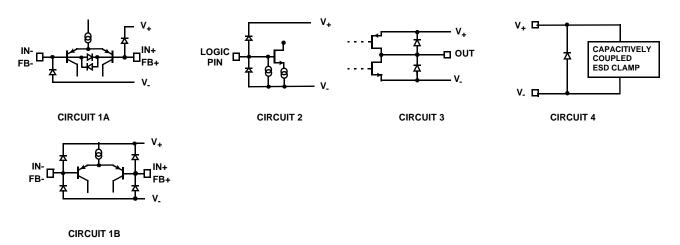

| ISL28270<br>16 Ld QSOP | ISL28273<br>16 Ld QSOP | ISL28470<br>28 Ld QSOP | PIN NAMES                     | EQUIVALENT<br>CIRCUIT     | PIN FUNCTION                                                                                                                                                                                                                                                           |

|------------------------|------------------------|------------------------|-------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2, 15                  | 2, 15                  | 1, 13<br>16, 28        | OUT_A, OUT_B,<br>OUT_C, OUT_D | Circuit 3                 | Output Voltage. A complementary Class AB common-source output stage drives the output of each channel. When disabled, the outputs are in a high impedance state                                                                                                        |

| 3, 14                  | 3, 14                  | 2, 12<br>17, 27        | FB+_A, FB+_B,<br>FB+_C, FB+_D | Circuit 1A,<br>Circuit 1B | Positive Feedback high impedance terminals. ISL28270 and ISL28470 input circuit is shown in Circuit 1A, and the ISL28273 input circuit is shown in Circuit 1B. It can be used as a REF terminal to adjust or level shift the output.                                   |

|                        |                        |                        |                               |                           | ISL28273: to avoid offset drift, it is recommended that the terminals of the ISL28273 are not overdriven beyond 1V and the input current must never exceed 5mA.                                                                                                        |

| 4, 13                  | 4, 13                  | 3, 11<br>18, 26        | FBA, FBB,<br>FBC, FBD         | Circuit 1A,<br>Circuit 1B | Negative Feedback high impedance terminals. The FB- pins connect to an external resistor divider to individually set the desired gain of the inamp. ISL28270 and ISL28470 input circuit is shown in Circuit 1A, and the ISL28273 input circuit is shown in Circuit 1B. |

|                        |                        |                        |                               |                           | ISL28273: to avoid offset drift, it is recommended that the terminals of the ISL28273 are not overdriven beyond 1V and the input current must never exceed 5mA.                                                                                                        |

| 5, 12                  | 5, 12                  | 4, 10<br>19, 25        | INA, INB,<br>INC, IND         | Circuit 1A,<br>Circuit 1B | High impedance Inverting input terminals. Connect to the low side of the input source signal. ISL28270 and ISL28470 input circuit is shown in Circuit 1A, and the ISL28273 input circuit is shown in Circuit 1B.                                                       |

|                        |                        |                        |                               |                           | ISL28273: to avoid offset drift, it is recommended that the terminals of the ISL28273 are not overdriven beyond 1V and the input current must never exceed 5mA.                                                                                                        |

| 6, 11                  | 6, 11                  | 5, 9<br>20, 24         | IN+_A, IN+_B,<br>IN+_C, IN+_D | Circuit 1A,<br>Circuit 1B | High impedance Non-inverting input terminals. Connect to the high side of the input source signal. ISL28270 and ISL28470 input circuit is shown in Circuit 1A, and the ISL28273 input circuit is shown in Circuit 1B.                                                  |

|                        |                        |                        |                               |                           | ISL28273: to avoid offset drift, it is recommended that the terminals of the ISL28273 are not overdriven beyond 1V and the input current must never exceed 5mA.                                                                                                        |

| 7, 10                  | 7, 10                  | 6, 8<br>21, 23         | EN_A, EN_B,<br>EN_C, EN_D     | Circuit 2                 | Active LOW logic pins. When pulled above 2V, the corresponding channel turns off and OUT is high impedance. A channel is enabled when pulled below 0.8V. Built-in pull-downs define each $\overline{\text{EN}}$ pin LOW when left floating.                            |

| 16                     | 16                     | 7                      | V <sub>+</sub>                | Circuit 4                 | Positive Supply terminal shared by all channels.                                                                                                                                                                                                                       |

### Pin Descriptions (Continued)

| ISL28270<br>16 Ld QSOP | ISL28273<br>16 Ld QSOP | ISL28470<br>28 Ld QSOP | PIN NAMES | EQUIVALENT<br>CIRCUIT | PIN FUNCTION                                                                           |

|------------------------|------------------------|------------------------|-----------|-----------------------|----------------------------------------------------------------------------------------|

| 8                      | 8                      | 22                     | V-        |                       | Negative Supply terminal shared by all channels. Grounded for single supply operation. |

| 1, 9                   | 1, 9                   | 14,15                  | NC        |                       | No Connect, pins can be left floating or grounded                                      |

# Application Information

# **Product Description**

The ISL28270 and ISL28273 are dual channel micro-power instrumentation amplifiers (in-amps) and the ISL28470 is a quad channel which deliver rail-to-rail input amplification and rail-to-rail output swing. The in-amps also deliver excellent DC and AC specifications while consuming only about 60µA per channel. Because the independent pair of feedback terminals set the gain and adjust the output zero level, the ISL28270, ISL28273 and ISL28470 achieve high CMRR regardless of the tolerance of the gain setting resistors. The ISL28270 and ISL28470 are internally compensated for a minimum gain of 100. The ISL28273 is internally compensated for a minimum gain of 10.

$\overline{\text{EN}}$  pins are available to independently enable or disable a channel. When all channels are off, current consumption is down to typically 4µA on the duals (ISL28270 and ISL28273), and 10µA on the quad (ISL28470).

#### **Input Protection**

All input terminals and feedback terminals have internal ESD protection diodes to both positive and negative supply rails, limiting the input voltage to within one diode beyond the supply rails. Input signals originating from low impedance sources should have current limiting resistors in series with the IN+ and IN- pins to prevent damaging currents during power supply sequencing and other transient conditions. The ISL28270 and ISL28470 have additional back-to-back diodes across the input terminals and also across the feedback terminals. If overdriving the inputs is necessary, the external input current must never exceed 5mA. External

series resistors may be used as an external protection to limit excessive external voltage and current from damaging the inputs. On the other hand, the ISL28273 has no clamps to limit the differential voltage on the input terminals allowing higher differential input voltages at lower gain applications. It is recommended, however, that the terminals of the ISL28273 are not overdriven beyond 1V to avoid offset drift.

#### Input Stage and Input Voltage Range

The input terminals (IN+ and IN-) of the in-amps are a single differential pair of bipolar PNP devices aided by an Input Range Enhancement Circuit, IREC, to increase the headroom of operation of the common-mode input voltage. The feedback terminals (FB+ and FB-) also have a similar topology. As a result, the input common-mode voltage range is rail-to-rail regardless of the feedback terminal settings and regardless of the gain settings. They are able to handle input voltages that are at or slightly beyond the supply and close to ground making these in-amps well suited for single 5V down to 2.4V supply systems. There is no need to bias the common-mode input to achieve symmetrical input voltage. It is recommended however that the common-mode input be biased at least 10mV above the negative supply rail to achieve top performance. See "Input Bias Cancellation/Compensation" on page 15.

The IREC enables rail-to-rail input amplification without the problems usually associated with the dual differential stage topology. The IREC ensures that there are no drastic changes in offset voltage over the entire range of the input. See Input Offset Voltage vs Common-Mode Input Voltage on page 8. IREC also cures the abrupt change and even reverse polarity of the input bias current over the whole

range of input. See Input Bias Current vs Common-Mode Input Voltage on page 8.

#### Input Bias Cancellation/Compensation

All three parts have an Input Bias Cancellation/Compensation Circuit for both the input and feedback terminals (IN+, IN-, FB+ and FB-), achieving a low input bias current throughout the input common-mode range and the operating temperature range. While the PNP bipolar input stages are biased with an adequate amount of biasing current for speed and increased noise performance, the Input Bias Cancellation/Compensation Circuit sinks most of the base current of the input transistors leaving a small portion as input bias current, typically 500pA. In addition, the Input Bias Cancellation/Compensation Circuit maintains a smooth and flat behavior of input bias current over the common mode range and over the operating temperature range. The Input Bias Cancellation/Compensation Circuit operates from input voltages of 10mV above the negative supply to input voltages slightly above the positive supply. See Input Bias Current vs Common-Mode Input Voltage in the "Typical Performance Curves" on page 8.

#### Output Stage and Output Voltage Range

A Class AB common-source output stage drives the output. The pair of complementary MOSFET devices drive the output VOUT to within a few millivolts of the supply rails. At a  $100 k\Omega$  load, the PMOS sources current and pulls the output up to 4 mV below the positive supply. The NMOS sinks current and pulls the output down to 4 mV above the negative supply, or ground in the case of a single supply operation. The current sinking and sourcing capability are internally limited to 29 mA. When disabled, the outputs are in a high impedance state.

#### Gain Setting

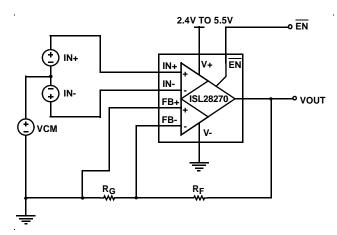

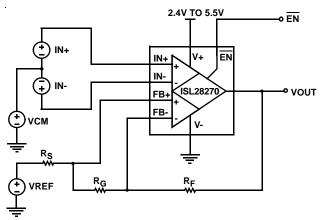

VIN, the potential difference across IN+ and IN-, is replicated (less the input offset voltage) across FB+ and FB-. The function of the in-amp is to maintain the differential voltage across FB- and FB+ equal to IN+ and IN-; (FB- - FB+) = (IN+ - IN-). Consequently, the transfer function can be derived. The in-amp gain is set by two external resistors, the feedback resistor  $R_{\rm F}$ , and the gain resistor  $R_{\rm G}$ .

$$VIN = IN + -IN -$$

$$VOUT = \left(1 + \frac{R_F}{R_G}\right) VIN \tag{EQ. 1}$$

In Figure 49, the FB+ pin and one end of resistor  $R_G$  are connected to GND. With this configuration, Equation 1 is only true for a positive swing in VIN; negative input swings will be ignored because the output will be at ground.

FIGURE 49. GAIN IS SET BY TWO EXTERNAL RESISTORS,  $\rm R_F$  AND  $\rm R_G$

#### Reference Connection

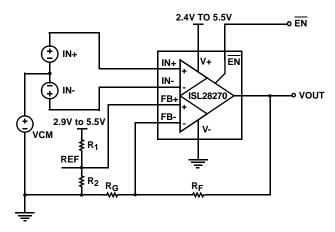

Unlike a three op amp in-amp realization, a finite series resistance seen at the REF terminal does not degrade the high CMRR performance, eliminating the need for an additional external buffer amplifier. Figure 50 uses the FB+ pin to provide a high impedance REF terminal.

FIGURE 50. GAIN SETTING AND REFERENCE CONNECTION

VIN = IN + -IN -

$$VOUT = \left(1 + \frac{R_F}{R_G}\right)(VIN) + \left(1 + \frac{R_F}{R_G}\right)(VREF)$$

(EQ. 2)

The FB+ pin is used as a REF terminal to center or to adjust the output. Because the FB+ pin is a high impedance input, an economical resistor divider can be used to set the voltage at the REF terminal without degrading or affecting the CMRR performance. Any voltage applied to the REF terminal will shift VOUT by VREF times the closed loop gain, which is set by resistors  $R_{\text{F}}$  and  $R_{\text{G}}$ . Note that any noise or unwanted signals on the reference supply will be amplified at the output according to Equation 2. See Figure 50.

The FB+ pin can also be connected to the other end of resistor, R<sub>G</sub>. See Figure 51. Keeping the basic concept that

the in-amp maintains constant differential voltage across the input terminals and feedback terminals (FB- - FB+) = (IN+ - IN-), the transfer function of Figure 51 can be derived from Equation 3. Note that the VREF gain term is eliminated, and susceptibility to external noise is reduced.

FIGURE 51. REFERENCE CONNECTION WITH AN AVAILABLE VREF

VIN = IN + -IN -

$$VOUT = \left[1 + \frac{R_S + R_F}{R_G}\right] + VREF$$

(EQ. 3)

$$VOUT = \left(1 + \frac{R_F}{R_G}\right)(VIN) + (VREF)$$

(EQ. 4)

A finite resistance  $R_S$  in series with the VREF source, adds an output offset of VIN\*( $R_S/R_G$ ). As the series resistance  $R_S$  approaches zero, Equation 3 is simplified to Equation 4 for Figure 51. VOUT is simply shifted by an amount VREF.

#### **External Resistor Mismatches**

Because of the independent pair of feedback terminals provided by the in-amps, the CMRR is not degraded by any resistor mismatches. Hence, unlike a three op amp and especially a two op amp in-amp realization, the ISL28270, ISL28273 and ISL28470 reduce the cost of external components by allowing the use of 1% or more tolerance resistors without sacrificing CMRR performance. The CMRR will be typically 110dB regardless of the tolerance of the resistors used. Instead, a resistor mismatch results in a higher deviation from the theoretical gain - gain error.

### Gain Error and Accuracy

The gain error indicated in the "Electrical Specifications" table on page 4 is the inherent gain error alone. The gain error specification listed does not include the gain error contributed by the resistors. There is an additional gain error due to the tolerance of the resistors used. The resulting non-ideal transfer function effectively becomes:

$$VOUT = \left(1 + \frac{R_F}{R_G}\right) \times \left[1 \pm \left(E_{RG} + E_{RF} + E_G\right)\right] \times VIN \tag{EQ. 5}$$

Where:

E<sub>RG</sub> = Tolerance of RG

E<sub>RF</sub> = Tolerance of RF

E<sub>G</sub> = Gain Error of the ISL28270

The term  $[1 - (E_{RG} + E_{RF} + E_G)]$  is the deviation from the theoretical gain. Thus,  $(E_{RG} + E_{RF} + E_G)$  is the total gain error. For example, if 1% resistors are used, the total gain error would be:

TotalGainError =

$$\pm (E_{RG} + E_{RF} + E_{G}(typical))$$

(EQ. 6)

TotalGainError =  $\pm (0.01 + 0.01 + 0.005) = \pm 2.5\%$

#### Disable/Power-Down

The ISL28270, ISL28273 and ISL28470 have an enable/disable pin for each channel. They can be powered down to reduce the supply current to typically  $4\mu A$  when all channels are off. When disabled, the corresponding output is in a high impedance state. The active low  $\overline{EN}$  pin has an internal pull-down and hence can be left floating and the in-amp enabled by default. When the  $\overline{EN}$  is connected to an external logic, the in-amp will shutdown when the  $\overline{EN}$  pin is pulled above 2V, and will power up when  $\overline{EN}$  is pulled below 0.8V.

#### **Unused Channels**

The ISL28270, ISL28273 and ISL28470 are dual and quad channel op amps. If the application only requires one channel when using the ISL28270, ISL28273 or less than 4 channels when using the ISL28470, the user must configure the unused channel(s) to prevent them from oscillating. The unused channel(s) will oscillate if the input and output pins are floating. This will result in higher than expected supply currents and possible noise injection into the channel being used. The proper way to prevent this oscillation is to short the IN+ and IN- terminals to ground and short the FB+, FB- and the output terminals to ground as shown in Figure 52.

FIGURE 52. PREVENTING OSCILLATIONS IN UNUSED CHANNELS

#### **Power Dissipation**

It is possible to exceed the +150°C maximum junction temperatures under certain load and power-supply conditions. It is therefore important to calculate the maximum junction temperature (T<sub>JMAX</sub>) for all applications to determine if power supply voltages, load conditions, or package type need to be modified to remain in the safe operating area. These parameters are related in Equation 7:

$$T_{JMAX} = T_{MAX} + (\theta_{JA} \times PD_{MAXTOTAL})$$

(EQ. 7)

#### where:

- P<sub>DMAXTOTAL</sub> is the sum of the maximum power dissipation of each amplifier in the package (PD<sub>MAX</sub>)

- PD<sub>MAX</sub> for each amplifier can be calculated as shown in Equation 8:

PD<sub>MAX</sub> =

$$2*V_S \times I_{SMAX} + (V_S - V_{OUTMAX}) \times \frac{V_{OUTMAX}}{R_L}$$

(EQ. 8)

#### where:

- T<sub>MAX</sub> = Maximum ambient temperature

- $\theta_{JA}$  = Thermal resistance of the package

- PD<sub>MAX</sub> = Maximum power dissipation of 1 amplifier

- V<sub>S</sub> = Supply voltage (Magnitude of V<sub>+</sub> and V<sub>-</sub>)

- I<sub>MAX</sub> = Maximum supply current of 1 amplifier

- V<sub>OUTMAX</sub> = Maximum output voltage swing of the application

- R<sub>L</sub> = Load resistance

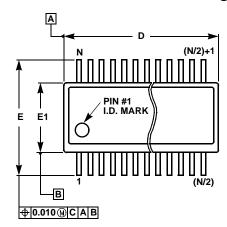

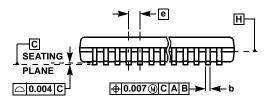

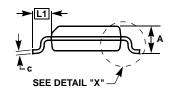

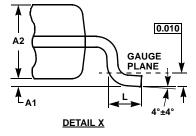

# Quarter Size Outline Plastic Packages Family (QSOP)

#### MDP0040

#### QUARTER SIZE OUTLINE PLASTIC PACKAGES FAMILY

|        |        | INCHES |        |           |       |

|--------|--------|--------|--------|-----------|-------|

| SYMBOL | QSOP16 | QSOP24 | QSOP28 | TOLERANCE | NOTES |

| Α      | 0.068  | 0.068  | 0.068  | Max.      | -     |

| A1     | 0.006  | 0.006  | 0.006  | ±0.002    | -     |

| A2     | 0.056  | 0.056  | 0.056  | ±0.004    | -     |

| b      | 0.010  | 0.010  | 0.010  | ±0.002    | -     |

| С      | 0.008  | 0.008  | 0.008  | ±0.001    | -     |

| D      | 0.193  | 0.341  | 0.390  | ±0.004    | 1, 3  |

| E      | 0.236  | 0.236  | 0.236  | ±0.008    | -     |

| E1     | 0.154  | 0.154  | 0.154  | ±0.004    | 2, 3  |

| е      | 0.025  | 0.025  | 0.025  | Basic     | -     |

| L      | 0.025  | 0.025  | 0.025  | ±0.009    | -     |

| L1     | 0.041  | 0.041  | 0.041  | Basic     | -     |

| N      | 16     | 24     | 28     | Reference | -     |

Rev. F 2/07

#### NOTES:

- Plastic or metal protrusions of 0.006" maximum per side are not included.

- Plastic interlead protrusions of 0.010" maximum per side are not included.

- 3. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com